Services

Odio et unde deleniti. Deserunt numquam exercitationem. Officiis quo odio sint voluptas consequatur ut a odio voluptatem. Sit dolorum debitis veritatis natus dolores. Quasi ratione sint. Sit quaerat ipsum dolorem.

Our Services

Realize next-gen chips and systems – on robust engineering

ASIC/FPGA Design

We offer specialized ASIC and FPGA development services, with expert engineers skilled in RTL design using Verilog, VHDL, and SystemVerilog. We develop IP based on specifications, optimizing for timing, area, and power, and provide seamless integration into larger subsystems or chips, including processors.

We specialize in assisting clients across various sectors, including AI-driven data centres, aerospace, automotive, networking, consumer electronics, industrial, medical, and IoT. Our team excels in digital and mixed-signal ASIC design, as well as FPGA-SoC development, catering to the growing demand for high-performance, low-power consumption, and compact form-factor designs. We leverage our strong expertise in mixed-signal solutions, covering design, verification, physical design, and validation, to deliver cutting-edge designs even at lower geometry nodes. With a proven track record, we have successfully taped-out over 250+ silicon designs, ranging from mature 180nm processes to cutting-edge 3nm and beyond. We take pride in being the first engineering services company to achieve tape-out at the revolutionary 7nm and 10nm nodes.

We have been part of many chip development projects where responsibilities included

- Architecture development

- RTL development and integration

- Synthesis for ASIC or FPGA and Static Timing Analysis

- FPGA implementation or ASIC prototyping

- Formal verification and equivalence checking

Functional Verification

Verification is crucial in silicon development, impacting quality, schedule, and cost. Tessolve, a chip design solution, offers extensive verification resources, tools, and methodologies to help semiconductor companies meet their validation needs.

We provide ASIC and FPGA functional verification services spanning the entire coverage-driven verification flow from specification to coverage sign-off. We have extensive experience in all major hardware verification languages (HVLS) such as e-Language and SystemVerilog, and methodologies such as UVM, OVM, VMM, and eRM.

We are proficient in the use of all major EDA vendor tools, such as Cadence Incisive® Enterprise Simulator, the Synopsys VCS® functional verification solution, and Mentor’s Questa® Advanced Simulator. We also use the Cadence® Palladium® series of accelerators/emulators, system-level modeling languages such as SystemC, and tools like MATLAB®.

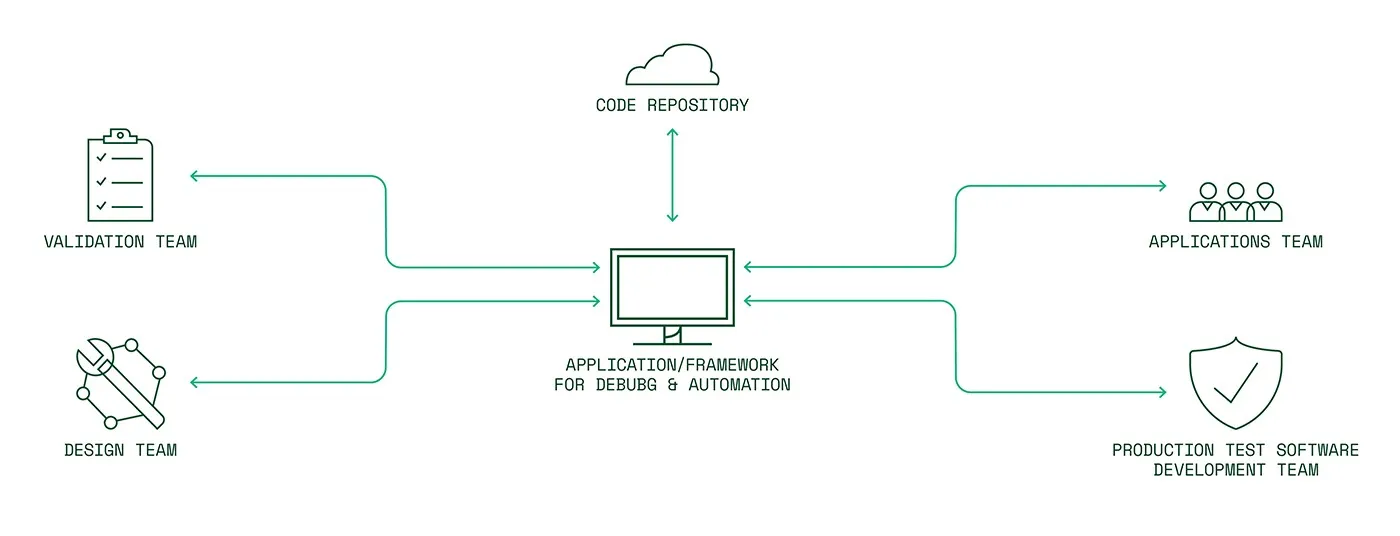

Post Silicon Validation

We specialize in identifying and validating features during pre- and post-silicon phases. In Post-Silicon Validation (PSV), we develop high-level test plans, collaborate with design engineers, and create algorithms for various test flows and documentation.

Our solution includes complete hardware design and software development. We enable hardware and software verification in the post-silicon bring-up phase using a well-defined Silicon Validation Services methodology and capabilities across the pre-silicon development cycle. These include electrical checks, device characterization, function and performance qualification, etc.

We consider ourselves for Identifying and making a list of features to be validated as part of pre & post-silicon validation. As a part of Post-Silicon Validation, we do work on the development of a High-level Test plan get it reviewed by design engineers and develop the algorithms for various test flow design documents and code. Applying software validation techniques in PSV is the key to solving the puzzle. This can provide a significant reduction in the validation schedule while also improving and monitoring the coverage requirement. We consider this as an art more than just a technical skill. At Faststream Technologies, we combine our expertise in the whole gamut of silicon realization to provide our customers with a whole spectrum of silicon validation services. We always aim to reduce the schedule and cost for silicon validation while ensuring the required functional coverage is achieved.

Analog Layout

We offer full custom analog IC layout services, with engineers who bring a deep understanding of analog IC design. Our expertise ensures optimized circuit performance, reliability, die size, and production yield. We provide block-level and chip-level layouts, delivering fully verified GDSII data ready for integration or foundry tape-out.

Risedge Semiconductors has deep expertise in Analog, Mixed-Signal (AMS Design) Wireless, and RF Design services. It covers amplifiers, signal condition, passive and active filter, PLLs, audio processing, low-noise design, micropower design, A/D, D/A conversion, and many more related areas. We have sound experience from DC to low GHz microwave frequencies. Besides this, we are prominent in designing wireless devices that operate in the 2.4 GHz Industrial, Scientific, and Medical ISM band.

Tools used for Analog and Mixed-Signal Design

- Cadence Virtuoso is used for Schematic Capture and Mask Design.

- Cadence Specter, Specter-RF, ADE, and Specter Multi-Mode Sim with Analog/Mixed-Signal (AMS Design) are used for Circuit simulation.

- Keysight ADS Momentum is 3-D planar EM simulation software used for RF circuit and antenna analysis

- Mentor Calibre is our primary tool for RC parasitic extraction and DRC and LVS checking

- MATLAB/SIMULINK is used for System Analysis modeling

- Faststream’s server farm provides more than enough power than is needed to simulate and check the largest analog cores and chip designs.

Physical Design

Physical design is a crucial phase in VLSI engineering where the structural netlist is handed over from the front-end design team to the back-end design team. This process results in the creation of a physical layout database that includes geometric design details for each physical layer, which is essential for establishing interconnections.

Physical design is the process of turning a design into manufacturable geometries. It comprises a number of steps, including floorplanning, placement, clock tree synthesis, and routing. Physical design begins with a netlist, which is synthesized from RTL. The netlist describes the components of a circuit and how they connect. Floorplanning is the first major step. It involves identifying which structures should be placed near others, taking into account area restrictions, speed, and the various constraints required by components. Partitioning divides a chip into functional blocks.

Placement determines the locations of each component or block on the die, considering timing and interconnect length. Clock tree synthesis involves inserting buffers or inverters such that the clock is distributed evenly to sequential elements in a design, minimizing skew and latency. Routing determines the paths of interconnects, including standard cell and macro pins. This stage completes all connections defined in the netlist, ideally in the most efficient way and without violating timing constraints. The final output of the physical design process is typically GDSII, a data format representing layout information.

RTL Design

We provide RTL design services, transforming product specifications into both IP and SoC developments. Offerings include: Standard and Complex IP Block Design and Development. RTL Quality Checks: Lint, CDC, Automated property checks, Low-power checks. SoC and Subsystem Integration, Clock and Reset design, Clock gating, Low-power chip design, UPF definition

Register transfer level (RTL) is an abstraction for defining the digital portions of a design. It is the principle abstraction used for defining electronic systems today and often serves as the golden model in the design and verification flow. The RTL design is usually captured using a hardware description language (HDL) such as Verilog or VHDL. While these languages are capable of defining systems at other levels of abstraction, it is generally the RTL semantics of these languages, and indeed a subset of these languages defined as the synthesizable subset. This means the language constructs that can be reliably fed into a logic synthesis tool that in turn creates the gate-level abstraction of the design that is used for all downstream implementation operations.

RTL is based on synchronous logic and contains three primary pieces namely, registers which hold state information, combinatorial logic which defines the nest state inputs, and clocks that control when the state changes.